Abstraktní

Pokud jde o schopnost integrovaných obvodů systému správy baterií (BMS IC) odolávat elektromagnetickému rušení (EMI), musíme hovořit o uspořádání kabeláže desek plošných spojů (PCB) a externích komponent (EC), což jsou klíčové role. . Nezapomeňte, impedance samotného BMS IC je také velký problém. Ve skutečnosti tato impedance podstoupí významné změny v důsledku funkce vyvažování baterie BMS IC. Konkrétně většina integrovaných obvodů BMS na trhu integruje funkci pasivního vyvažování baterie, která výrazně snižuje impedanci představovanou integrovanými obvody BMS. Účelem naší studie je porozumět dopadu různých metod pasivního vyvažování baterií na imunitní úroveň BMS IC. Poté jsme také navrhli novou architekturu IC BMS, která nejen snižuje počet externích komponent, ale také maximalizuje dopad pasivního vyvažování baterie na imunitu IC, tedy úroveň vstřikování při testování přímého vstřikování energie (DPI). Tímto způsobem, dokonce i v hlučném prostředí, může IC udržovat vysoce přesná měření vysokého napětí.

1. Úvod

Lithium-iontové (Li Ion) baterie a systémy správy baterií (BMS) byly široce studovány s cílem připravit cestu pro novou generaci elektrických vozidel (EV) a hybridních elektrických vozidel (HEV). Například hlavním aspektem vývoje je charakterizovat elektromagnetické rušení (EMI) vedené z měniče měniče, což je jeden ze zdrojů šumu, který může způsobovat rušení IC BMS. V této šumové cestě mají kabely, směrování desek plošných spojů a externí komponenty (EC) významný vliv na imunitu IC BMS. EC, na které se zde zaměřujeme, jsou vysokonapěťové kondenzátory pro automobily používané k zabránění elektrostatickým výbojům (ESD). Jak bylo ukázáno v předchozí práci, nejlevnější konfigurací pro tyto EC jsou diferenciální připojení mezi bateriemi. To však povede ke zvýšení úrovně vstřikování v důsledku zavedení rezonance ve frekvenčním rozsahu přímého vstřikování energie (DPI) ([150 kHz; 1 GHz]), což je způsobeno konstruovanou sítí CL ladder.

V tomto případě pasivní vyvažování baterie spojí vyrovnávací odpor baterie a některé parazitní komponenty paralelně s ESD kondenzátorem, když je aktivován, což může změnit úroveň útlumu těchto rezonancí. Tato studie zvažuje dvě metody vyvažování baterie. První metodou je vyloučit baterii aktuálně měřenou IC BMS, zkratovat všechny baterie, které mohou být zkratovány, a poté extrahovat úroveň vstřikování měřené baterie během DPI, aby se vyhodnotil dopad této metody na imunitu IC. Kromě toho tato studie porovnávala dvě architektury používající tuto první balancovací metodu, přičemž hlavním rozdílem je počet baterií, které lze současně vyvažovat. Druhou metodou vyvažování je zkratování stejné baterie, která je aktuálně měřena integrovaným obvodem ve speciálně navržené architektuře. Navíc díky novému umístění balančních odporů navrhovaná architektura mění ESD kondenzátor na filtr, který umožňuje vyvážení pro výrazné snížení impedance pozorované na straně BMS, čímž se snižuje úroveň vstřikování. Kromě toho, aby bylo možné vyhodnotit vliv parazitní indukčnosti, byl také posouzen vliv vyvážení baterie v různých vzdálenostech mezi ESD kondenzátory a integrovanými obvody.

Nakonec je struktura tohoto článku následující: Nejprve je představeno modelování prostředí BMS IC; Za druhé, pomocí první metody vyvažování baterie porovnejte vliv vyvažování na úroveň vstřikování mezi dvěma architekturami BMS IC během DPI; Za třetí, představte navrhovanou architekturu a vyhodnoťte její dopad na vyvážení úrovně vstřikování během DPI pomocí druhé metody vyvážení.

2. Modelování prostředí integrovaného obvodu BMS

Funkce BMS a testování DPI:Hlavním účelem BMS je zajistit optimální a bezpečný provoz baterií v drsném prostředí elektromagnetického rušení (EMI). Některé z hlavních funkcí BMS IC zahrnují přesné měření napětí baterie a pasivní vyvažování baterie, aby se zabránilo degradaci baterie a dosáhlo se optimálního odběru energie z baterie. Aby bylo možné charakterizovat schopnost integrovaných obvodů provádět tyto úkoly v drsných prostředích EMI, bylo provedeno testování přímého vstřikování energie (DPI) připojením výkonu 30 dBm v běžném režimu (CM) ke všem vstupům integrovaného obvodu připojeným k baterii.

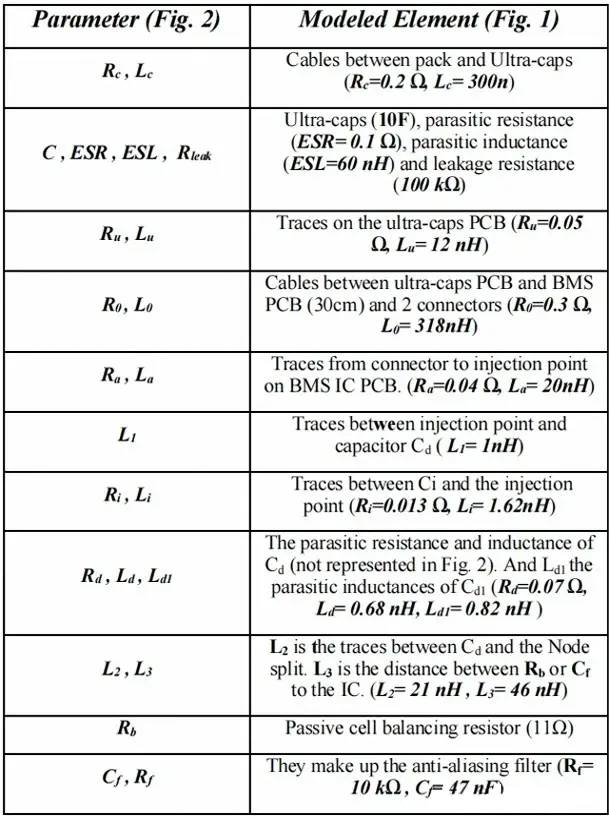

Nastavení testu DPI a související komponenty:Obrázek 1 ukazuje nastavení DPI použité v této studii s použitím produktu BMS IC, který může monitorovat až 18 baterií. Toto nastavení zavádí superkondenzátory pro konstrukci bateriových sad s napětím vyšším než 80 V pomocí 12V baterií a stabilizuje impedanci na straně bateriové sady. Z obrázku 1 je vidět, že současné metody modelování se zaměřují na prvky, jako je baterie a 30cm kabely na každé straně PCB, superkondenzátory, konektory, kabeláž PCB na desce superkondenzátoru a desce IC BMS, externí komponenty (EC ) na desce IC BMS a impedance prezentovaná samotným BMS.

Modelování prostředí BMS IC:Na obrázku 2 je vstup IC BMS modelován kondenzátorem C {L} (30pF) představujícím vnitřní pasivní vyvažovací spínač baterie se spínacím odporem Ron=0,25 Ω. Kondenzátor C {d} (47nF) používaný pro účely ESD je předmětem zájmu EC, který využívá nejlevnější konfiguraci. Model také zahrnuje parazitní odpor a indukčnost C {d} (parazitní odpor R {d} nabývá hodnot při frekvencích 100MHz a výše), přičemž je uvažováno parazitní chování injektovaného kondenzátoru C {i} (330pF). Vzhledem k přítomnosti relativně vysokých hodnot kapacity C {d} nebyl uvažován kapacitní vliv vedení kabelů a desek plošných spojů. Baterie je modelována pomocí ideálního zdroje napětí, protože baterie a kabely jsou zkratovány superkondenzátory. Všechny parametry 18 baterií na obrázku 2 jsou podobné, ignorujíce nesoulad ve vzdálenosti mezi každou baterií a kolíkem IC. Tento model je účinný v rozsahu [150 kHz, 200 MHz].

IC pin a situace související s architekturou:V architektuře 1 je pin C {Bx} používaný pro měření napětí baterie a pasivní vyvažování baterie, stejně jako pin C {Tx} používaný pouze pro měření napětí redundance baterie. Měření přes pin C {Tx} je prováděno diskrétním analogově-digitálním převodníkem (DT ADC), proto je vyžadován antialiasingový filtr (AAF, tj. R {f} a C {f}); Měření přes pin C {Bx} je prováděno kontinuálním analogově-digitálním převodníkem (CT ADC) bez potřeby AAF. Další část představí architekturu 2 a první vyrovnávací metodu použitou v této studii ke zlepšení imunity BMS IC. Bude také porovnávat útlum úrovně vstřikování, který přináší první metoda pasivního vyvažování baterie mezi architekturou 1 a architekturou 2. Kromě toho tato studie předpokládá, že aktivace rovnováhy baterie trvá několik set mikrosekund, což je dostatečné pro měření napětí zainteresované baterie , a proto nebude mít významný vliv na stav nabití rovnovážné baterie.

3. Rozdíly v architektuře IC BMS, problémy s rezonancí a dopad první metody vyvažování

Architektonické rozdíly a jevy rezonance:Uspořádání pinů integrovaných obvodů BMS, počet a typ použitých analogově-digitálních převodníků (ADC) a další architektonické aspekty přímo ovlivňují externí komponenty. V architektuře 1 (obrázek 2), s výjimkou C_{B0} a C_{B19}, je každý pin C_{Bx} sdílen dvěma baterie. Vzhledem k nutnosti nastavit R_ {b} na každé stopě PCB vedoucí k pinu C{{10}}}{Bx} při testování DPI, aby se omezil převod z běžného režimu (CM) do diferenciálního režimu (DM), sousední baterie nemohou být vyváženy současně a liché a sudé baterie musí být vyváženy v různých obdobích. Architektura 2 (obrázek 3) má další kolík C {Bx \ _ H}, který může současně vyvažovat sousední baterie, ale zvětší velikost čipu, počet kolíků a externí komponenty (R {b}). Lichoběžníková síť CL složená z L_ {T} (L_ {u}+L_ {0}+L_ {a}) a C_d} budou generovat více rezonancí, které mají relativně nízké frekvence (pod 10 MHz). V praktických aplikacích může kabel spojující BMS IC a baterii dosáhnout 2 metry, což sníží rezonanční frekvenci a zvýší faktor kvality. Ačkoli R_ {T} (R_ {u}+R_ {0}+R_ {a}) může do určité míry utlumit rezonanci, účinek je nedostatečný.

První metoda vyvažování a její dopad na úroveň vstřiku:První metodou vyvažování, kterou tato studie uvažuje, je extrahování špičkového napětí první baterie (C_{L1}) v simulaci DPI při vyvažování ostatních baterií. Pro architekturu 1 jsou vyváženy pouze baterie s lichým číslem (kromě baterie 1), protože vyvážení baterií se sudým číslem (počínaje baterií 2) by změnilo stejnosměrný proud (DC) baterie 1, což není v souladu se skutečnými scénáři měření. U architektury 2 mohou být všechny baterie kromě baterie 1 vyvážené. Vyhodnoťte provedením simulací přechodných jevů v prostředí koření (poskytnutí dostatečné periodové stability signálu, extrahování průměrného špičkového napětí za určitou periodu a získání dostatečného počtu bodů v rozsahu [150 kHz; 200 MHz]). Výsledky ukázaly, že pasivní vyrovnání baterie snížilo amplitudu rezonance, jak se očekávalo při nízkých frekvencích, ale zvýšilo úroveň vstřikování při vysokých frekvencích (přibližně 150 MHz). Architektura 2 má větší vliv na úroveň vstřikování díky vyrovnávání baterií při nízkých frekvencích, protože dokáže vyvážit více baterií současně a zavést větší tlumení; Při vysokých frekvencích je její vlastní úroveň vstřikování nižší než u architektury 1 a po aktivaci vyvážení baterie dochází pouze k mírnému zlepšení vysokých frekvencí. Kromě toho existuje kompromis mezi hodnotou vyrovnávacího odporu baterie $R_ {b} $a úrovní vstřikování. Snížení R_ {b} zvýší útlum nízkofrekvenční rezonance, ale zeslabí útlum vysokofrekvenční rezonance, zatímco zvýšení R_ {b} bude mít opačný účinek.

4. Analýza 2. rovnovážné metody a návrh nové architektury

Analyzujte ideální scénáře a strategie zlepšování:Chcete-li vyhodnotit dopad vyvažování baterie na nízkofrekvenční rezonanci, analyzujte ideální a zjednodušený scénář (podobný architektuře 1, ale zjednodušený). Při frekvencích pod 5 MHz lze superkondenzátory považovat za zkraty kvůli jejich vysoké kapacitní hodnotě (10F) a parazitním parametrům (ekvivalentní sériový odpor ESR, ekvivalentní sériová indukčnost ESL), které jsou v tomto rozsahu nízké; Při zvažování nízkofrekvenční rezonance lze C {L} ignorovat; Pro analýzu je vhodné použít jednoduchou lichoběžníkovou síť bez vnější zátěže. Pro celkovou impedanci v tomto scénáři (vzorec 1) byla rezonanční frekvence vypočtena pomocí specifického výrazu (vzorec 2). Bylo zjištěno, že za daných parametrů je diskriminant formule 2 záporný se dvěma pomyslnými kořeny a reálná část odráží rezonanční útlum (pseudoperiodický stav, formule 3). Pro zjednodušený implementační scénář vyvažování baterie na obrázku 7b byl vypočten polynom rezonance (vzorec 4). Bylo zjištěno, že co možná největší snížení odporu R může učinit diskriminativnější vyjádření rezonančního indexu kladným, což významně zeslabuje rezonanční frekvenci, ale některé rezonance jsou stále v pseudoperiodickém stavu. Faktor útlumu (vzorec 5) udává, že pokud je R dostatečně nízké, vyvážení baterie může významně ovlivnit úroveň vstřikování. I když zvýšení odporu může zlepšit R_ {T}, není to možné pro architektury 1 a 2, protože to sníží přesnost měření pinu C_ {Tx} během vyvažování baterie.

Navrhněte novou architekturu a hodnocení výkonu:Navrhněte novou architekturu, ve které měření pinu C {Tx} využívá spojitý analogově-digitální převodník (CT ADC) bez potřeby antialiasingových filtrů (AAF, tj. R {f} a C {f}) , měření pinu C {Bx} používá diskrétní analogově-digitální převodník (DT ADC) a balanční rezistor R {b} se přesune před ESD kondenzátor C {d}, čímž se šetří součástky a zesílení nízkofrekvenčního rezonančního útlumu. Aby se předešlo chybám měření při vyvažování baterie, je měření C {Tx} provedeno před R {b}. Druhá metoda vyvažování vyrovnává měřenou baterii (jako je článek x, obrázek 8), aby se snížila úroveň vstřikování kolíku C {Tx}. Nová architektura maximalizuje dopad vyvažování baterie na úroveň vstřikování DPI umístěním R {b} před C {d} a přiblížením C {d} blíže k IC. Výsledky simulace ukazují, že nová architektura má nižší vlastní úroveň vstřikování než stará architektura, když není aktivováno vyvažování baterie (obrázek 5), a lze dosáhnout významného útlumu, když je C {d} umístěn v rozumné vzdálenosti od IC ( 0.5 cm nebo 1 cm) (obrázek 9). V nové architektuře však existuje kompromis ve výkonu ESD. V architektuře 1 a 2, když dojde k ESD události, C {d} poskytuje nízkoimpedanční zemní cestu pro kolík, zatímco v nové architektuře R {b} představuje vysoké napětí pro kolík C {Tx}. Proto R {b} potřebuje zvolit vhodnou hodnotu nebo umístit vnitřní upínací zařízení na C {Tx}, aby se problém zmírnil. Budoucí práce se zaměří na zlepšení výkonu ESD nové architektury.

5. Shrnutí

Tato studie navrhuje model integrovaného obvodu systému řízení baterie (BMS IC) pro praktickou simulaci přímého vstřikování energie (DPI), navrhuje první metodu vyvažování baterie pro snížení úrovně vstřikování během DPI a porovnává výkon dvou architektur v rámci této metody. Vytvořením jednoduchého analytického modelu, zkoumáním dopadu vyvažování baterií na úroveň útlumu nízkofrekvenční rezonance a stanovením strategií pro snížení vazby nízkofrekvenčního důležitého šumu. Navrhněte novou architekturu, která snižuje počet externích součástí a úrovně vstřikování, čímž je vyvážení baterie důležitější pro imunitu IC.

Nová architektura má kompromisy související s výkonem elektrostatického výboje (ESD). Budoucí práce se zaměří na vyhodnocení výkonu ESD nové architektury a prozkoumání možných opatření ke zlepšení bez nadměrného navyšování počtu externích komponent, s cílem optimalizovat celkový výkon nové architektury, lépe ji aplikovat na praktické systémy správy baterií, zlepšit výkon systému z hlediska elektromagnetické kompatibility, zajištění stabilního provozu systému správy baterií ve složitých elektromagnetických prostředích a vyvážení nákladů a výkonu.